也许很多新手都有想过如何利用FPGA做一个VGA电子相框之类的项目,或者需要用到SDRAM作为外设存储器的其他项目,但由于接触FPGA时间不长,虽认真研读过各种关于SDRAM的资料,却仍然无法使用Verilog设计出一个工作正常的SDRAM控制器。

在本文中,【开源骚客】将会先引入一个SDRAM控制器简单例子的演示视频(串口控制SDRAM的读写)。随后,将给大家介绍该项目中各个模块的功能划分。让大家也可以轻松设计出一款完全为自己定制的SDRAM控制器。

项目演示视频

这个项目总的来讲,就是设计一个简单的SDRAM控制器,PC机通过串口发送指令和数据来控制SDRAM芯片实现任意读写操作。

本文主要通过以下几个部分进行讲解:

- 项目整体框图介绍;

- 串口收发模块讲解;

- SDRAM控制器核心模块。

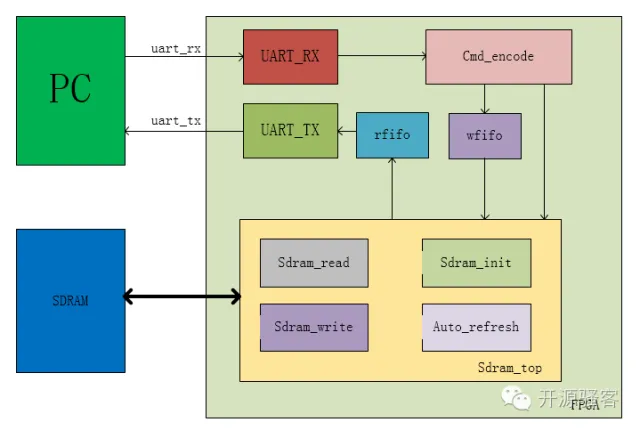

一、项目整体框图介绍

根据演示视频中的介绍,串口发送的第一个字节55表示写命令,第6个字节aa表示读命令,第二~第五个字节表示往SDRAM写入的数据。

接下来,我们模拟一下整个项目的数据流向及处理过程。

PC机通过串口发送数据给FPGA,FPGA内部的串口接收模块将接收到的数据传给Cmd_encode模块进行处理。 Cmd_encode模块对接收到的数据进行指令与数据分离,将数据写入wfifo,指令给SDRAM。 在SDRAM_TOP模块接收写指令后,会判断SDRAM目前的操作状态是否可以进行写状态,进入写状态后,读取wfifo中的数据并将其写入SDRAM。 而后,SDRAM_TOP模块接收到读指令,依然会判断SDRAM当前的操作状态是否可以进入度状态,进入读状态后,将SDRAM中的数据读出,并写入rfifo。 数据读出后,通过UART_TX模块发送给PC机。

对于这个项目中,使用wfifo和rfifo的目的是什么呢?之前Kevin在【开源骚客】公众号中有这样的一个活动,回答该问题,我们将免费赠送一本详细介绍串口收发模块设计的电子书。此活动长期有效。。。。只要你关注开源骚客公众号在后台进行回答,我们同样会赠送该电子书给您。

(注意:是只要你在后台回答哦,不管回答得正确与否,我们都会赠送电子书哦,书中附有详细代码!!!!!就是这么任性。。。。。。)

这本电子书是【开源骚客】公众号创始人Kevin凭借自身学习与工作经验总结的哦!!!!

二、串口收发模块讲解

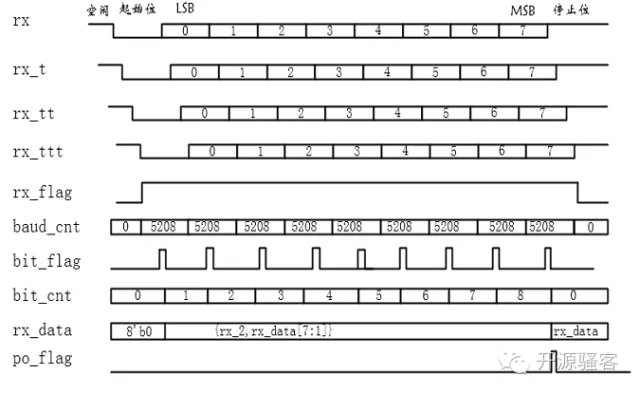

由于PC机通过串口发送的时钟域与FPGA内部工作的时钟域不一样,所以首先需要进行跨时钟域处理,对rx进行打两拍处理。 (开源骚客创始人Kevin在博客中有对跨时钟域的几种方法做详细介绍,) rx_ttt是对rx的3级寄存器,用于检测rx的起始位。当检测到起始位之后,rx_flag串口接收标志拉高,波特率计数器开始工作,当波特率计数器计数到2604(FPGA工作时钟为50MHz)时,bit_flag拉高,rx_data进行锁存接收到的串口数据。当bit_cnt计数器为8时,即表示串口的一帧数据接收完毕。

三、SDRAM控制器核心模块介绍

本项目中,SDRAM控制器分了5个模块进行设计:

SDRAM_TOP:仲裁老大,控制SDRAM各个操作的执行;

SDRAM_INIT:SDRAM初始化模块,设置SDRAM突发长度、潜伏期等;

AUTO_REFRESH:自刷新模块,为确保SDRAM保存的数据不丢失,自动刷新;

SDRAM_WITE:SDRAM写模块,接收到命令后将数据写入;

SDRAM_READ:SDRAM读模块,接收读命令后,将数据读出。

特别提醒#1 【开源骚客】团队目前已录制《轻松设计SDRAM控制器》系列视频教程五讲内容,并收获了一致好评。

视频教程在线观看地址:http://t.elecfans.com/1418.html

百度网盘下载地址:[url=]http://pan.baidu.com/s/1o88h0Ps[/url] 密码:t9qg

加入QQ群,Kevin为你解决疑惑:312109973 本文内容版权归【开源骚客】所有,转载请注明出处!!!!

|

/1

/1

|手机版|OpenEdv-开源电子网

( 粤ICP备12000418号-1 )

|手机版|OpenEdv-开源电子网

( 粤ICP备12000418号-1 )