|

高速先生成员--黄刚 相信高速先生的粉丝都知道我们有差不多上千的设计工程师了吧。既然有那么多人,那么每天发生点奇奇怪怪的案例就是很不奇怪的事情了!一天下午,Chris正愁着下周不知道给大家看点啥文章的时候,百无聊赖中翻翻之前的案例,找到多年之前的一个看起来很正常,揭秘起来又感觉很有趣的高速设计案例,决定拿出来给大家分享下,让我们成千上万的粉丝一起后怕起来。

是的,我相信这个设计的确是很常见的做法,十个设计工程师可能有5个都曾经这样做过。相信Chris一说出来,你们立马就要对号入座了。想当年,这事情的开头是源自于我司某分部的资深设计同事C君给Chris发过来的信息。

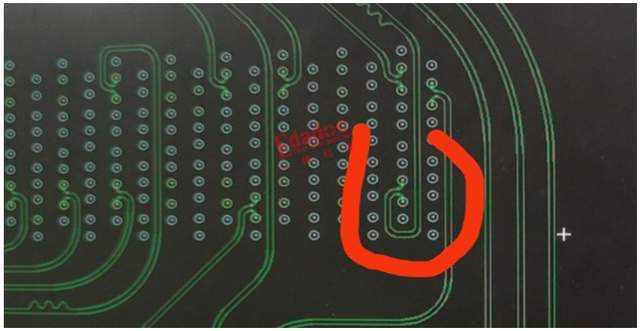

小图片看不清是什么设计是吧,Chris也一样。当Chris把它点开之后,哦!!!原来是在高速连接器扇出的走线设计,大家也觉得很普通吧!

无非就是出线通道可能被挡住了,只能从下面绕一下再往上扇出呗。再给大家看一张整体的出线图,大家就明白了。的确,很多工程师都会这样扇出。

Chris一直都是个对技术很执着的人,这个虽然不是仿真的项目,也毫不犹豫的拿过来,打算自己验证下到底有没有影响。毕竟这对信号的速率是高达28Gbps,而且Chris其实也是觉得会有影响的。

二话不说,拿到板子之后,Chris就专门针对这种绕着连接器走的信号进行了3D的建模,就是下面这个样子了。

经过七七二十一分钟的仿真时间后,仿真结果出来了。从损耗的结果上看,也没什么异常啊!

虽然不是非常非常线性,但是在28Gbps用到的频段内也还是不错,损耗大概1.5dB的样子,然后在很高频后才有明显的跌落。那大家就放心了嘛,原来Chris验证之后的确也没有很严重的问题嘛。

咋滴,文章就这样完了?那当然不会啦,这样显得多没意思啊!上面的结果看起来是没有很致命的影响,但是没有经过和好的设计对比,你怎么知道它没有伤害呢?关键是问题来了,怎么才能有一个和它能对比的好的设计呢?

也没那么难了,大家应该都公认的不在连接器里面绕一圈,直接扇出应该算好的设计了吧。然后我们把直接扇出的走线长度做成了绕线的长度一样,那就是一组很有价值的对比模型了,就像下面这样。

又过了七七二十一分钟,对比的仿真结果也出来了。果然经不起对比,上面绕线的结果瞬间让人觉得还是很差的哦。在28Gbps速率对应的频率下,好的case损耗才0.5dB,足足好了1dB。如果速率再往上提的话,差距可能就是3dB,5dB以上了,这就是很大的差异了哦。

果然,作为SI工程师,的确需要有这个直觉。在速率慢慢变高的情况下,你只要发现和平时常见的设计不一样的情况,都要抱着怀疑的态度,从理论到仿真去进行验证。不要以为串扰只会发生在信号与信号之间,而忽略了信号本身对自己带来的影响。算你们运气好,这个case从影响程度上看,对28Gbps以下的信号还不算致命,实在没空间走线,这样做下也不一定会出啥功能的问题,再高些速率就危险了哦! 问题:到底这种在连接器过孔区域绕着出线的设计为什么高频性能会变差呢,说说你们的想法?

关于一博科技: 一博科技成立于2003年3月,深圳创业板上市公司,股票代码: 301366,专注于高速PCB设计、SI/PI仿真分析等技术服务,并为研发样机及批量生产提供高品质、短交期的PCB制板与PCBA生产服务。致力于打造一流的硬件创新平台,加快电子产品的硬件创新进程,提升产品质量。

|

/1

/1

|手机版|OpenEdv-开源电子网

( 粤ICP备12000418号-1 )

|手机版|OpenEdv-开源电子网

( 粤ICP备12000418号-1 )