|

高速先生成员--姜杰 地址信号一驱五的DDR4拓扑很常见,可是,一驱五拓扑还要求单DIE、双DIE颗粒兼容的你有见过吗? 案例开讲之前,先简单介绍下DIE,英语学的好的同学都知道这个词的意思不太吉利,不过,芯片设计领域的DIE(裸晶)是另外一个意思,它通常指的是芯片内部一个单独的晶圆区域,包含了芯片的一个或一组完整功能单元,大致可以理解为去掉了封装和引脚的芯片。芯片根据功能和规模由一个或多个DIE构成。

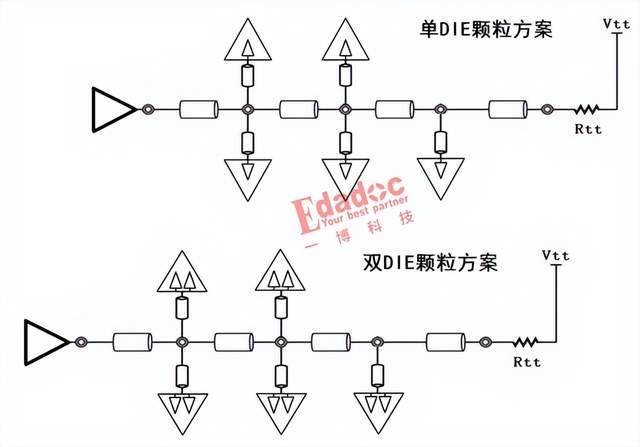

了解了芯片DIE的概念,相信各位已经能意识到我们这个案例兼容双DIE颗粒的难度了,没错,相比于单DIE方案,双DIE方案相当于接收端数量直接翻番,信号路径更加复杂,负载也更重,信号质量的恶化基本可以预见。

让高速先生略感欣慰的是,客户也认可双DIE颗粒的实现难度,因此,可以在保证单DIE颗粒3200Mbps速率的基础上,再考虑兼容双DIE颗粒。 遇到如此善解人意的客户,高速先生丝毫没有放松,首先对一驱五拓扑的单DIE颗粒方案进行优化。熟悉高速先生文章的同学一定还记得,对于一驱多Clamshell拓扑而言,反射会在靠近主控芯片处的近端颗粒处积累,因此,我们会重点关注信号质量较差的近端颗粒。原始眼图确实不尽如人意,无论是信号质量还是时序,都满足不了协议要求。

通过对PCB设计进行一系列的优化,近端信号质量大有改善。

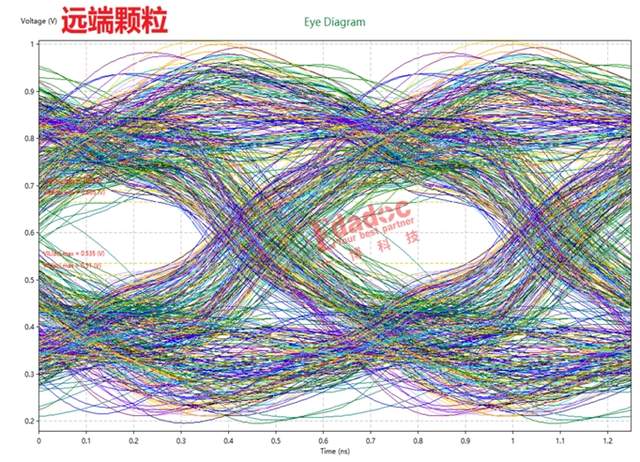

不得不说,眼见信号质量由坏变好,高速先生还是蛮有成就感的。只不过,愉悦的心情没有持续太久,因为很快就看到了当前设计上的双DIE颗粒仿真结果。和预期的一样,双DIE颗粒的信号质量惨不忍睹,连信号质量最好的远端颗粒都达不到有效眼高。

不过,通过观察对比,还是能发现双DIE颗粒容性较大的特点,下面是单DIE方案的远端颗粒眼图,相比上图,信号的上升沿明显陡峭很多。

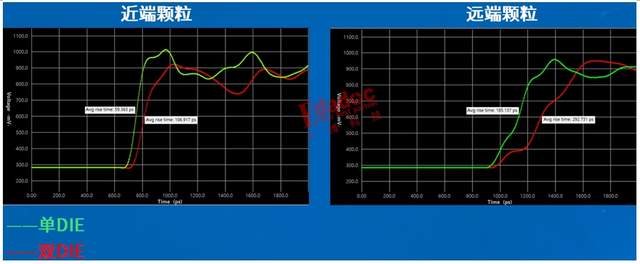

为了能更清楚的说明这个问题,高速先生分别在近端和远端对比了单、双DIE颗粒在相同激励下的信号上升时间。

通过比较,我们可以得到两个信息:一是对于不同类型的颗粒,双DIE颗粒容性更强,对信号上升沿衰减更大;二是对于相同类型的颗粒,由于容性负载效应,远端颗粒的上升沿衰减比近端颗粒大。 接下来的事情就是针对双DIE颗粒的拓扑进行设计优化了。在仿真过程中,高速先生发现,适用于单DIE颗粒的端接电阻Rtt阻值,却未必能用在双DIE颗粒的方案上。比如,对于单DIE颗粒,Rtt 33.2ohm时信号质量优于Rtt 24.9ohm的情况;而对于双DIE颗粒,Rtt 24.9ohm时信号质量却比Rtt 33.2ohm时要好。

关于端接电阻对DDR地址信号的影响,高速先生之前专门写过一篇文章,感兴趣的同学可以看看《端接电阻没选对,DDR颗粒白费?》 和以往的剧情不同,对于该案例的双DIE颗粒,虽然尝试了各种优化方法,最终也未能找到一个两全其美的兼容方案,客户无奈接受了双DIE颗粒需要降频的现实。 本案例一方面说明了没有万能的拓扑,同样的设计,不同DDR颗粒的结果可能不同;另一方面,从积极的角度来看,不同的主控芯片、不同的颗粒数量,对结果也都会有影响,所以,本案例无法实现并不代表其它案例的单、双DIE兼容无法达成。 回到本文题目的问题,相信大家已经有了答案。仿真不是万能的,比如这个案例中的双DIE方案;仿真也不是没有用,比如本案例中的单DIE方案,经过仿真优化才最终达到目标速率。总而言之一句话,道阻且长,仿真护航。

|

/1

/1

|手机版|OpenEdv-开源电子网

( 粤ICP备12000418号-1 )

|手机版|OpenEdv-开源电子网

( 粤ICP备12000418号-1 )