|

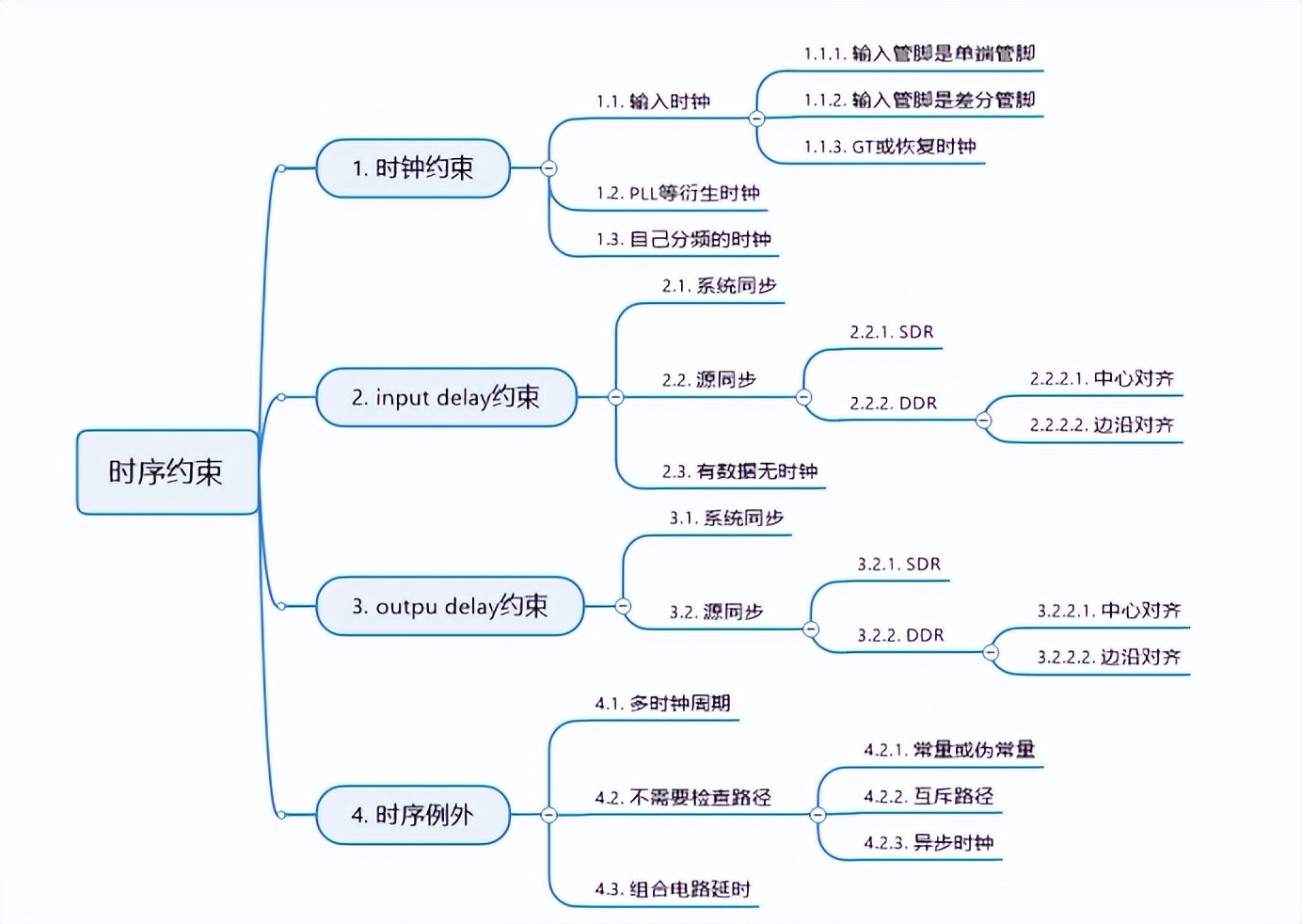

本文为明德扬原创文章,转载请注明出处! 本文章探讨一下FPGA的时序约束步骤,本文章内容,来源于配置的明德扬时序约束专题课视频。 时序约束是一个非常重要的内容,而且内容比较多,比较杂。因此,很多读者对于怎么进行约束,约束的步骤过程有哪些等,不是很清楚。明德扬根据以往项目的经验,把时序约束的步骤,概括分成四大步,分别是时钟的约束、input delays的约束、output delays的约束和时序例外。 时序约束是有先后的,首先要做时钟约束、其次是input delays约束、再次是output delays约束,最后才是时序例外的约束。这是一个完整的大步骤,也就是说我们在项目开始阶段就可以约束我们的时钟,把我们时钟的频率、周期、来源等等定义好。这一步做完之后,先不要做二三四步。这时候我们要完成我们的设计,要把我们内部的时序都完成之后才做第二步设置“input delays”,比如说我们从外部进来的一个情况。第三步output delays,也就是说要往下游器件发送的一个时序情况。当这一二三步都做完之后,我们在最后项目的阶段才做一个时序例外的情况。时序例外也就是说哪些时序是不需要分析的,这种情况要设置好。最后我们才能把整个时序约束完成。 以上是大的步骤,但事实上每一个步骤又可以细分成很多种情况。例如时钟约束,时钟可以分很多种,一种是差分时钟,一种是管脚进来的时钟、还有我们PLL产生时钟等等。还有一种是有数据但没有时钟的情况。input delays、output delays 也有很多种,我们到底要怎么样去分析,怎么去看。明德扬就把这四个步骤再进行细化,就是根据情况来分别列出来。

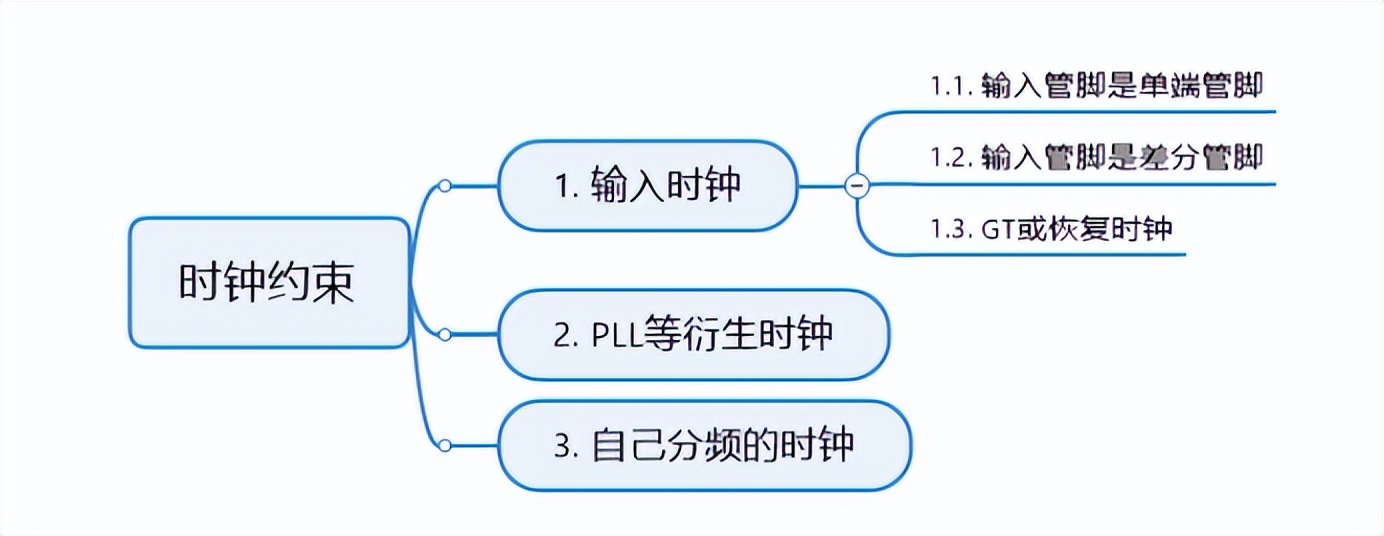

下面分别展开描述。 第1节 时钟 时钟约束可以分成很多种情况,不同的情况就有不同的约束方法,一般有哪几种情况呢?

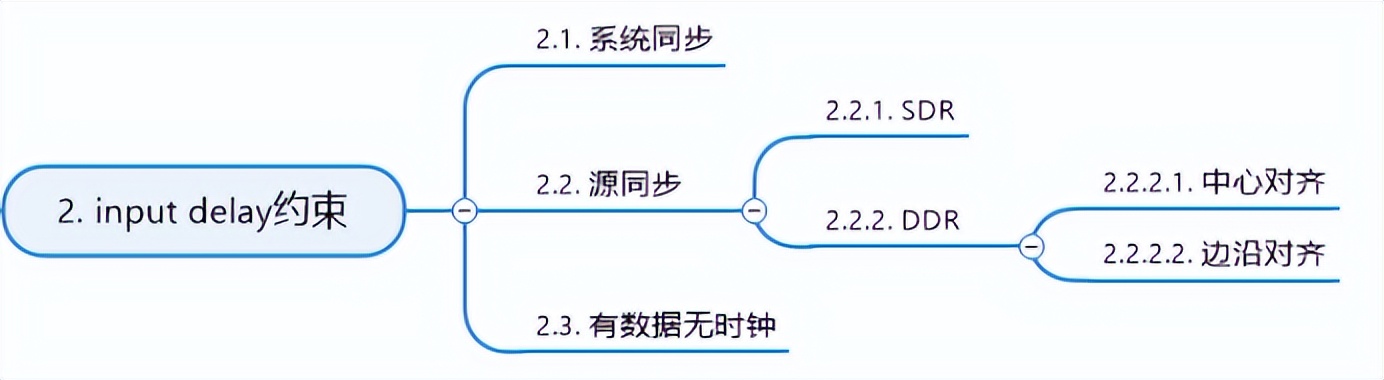

如上图,时钟约束概括地,可以分成三种情况,分别是输入时钟、PLL等衍生时钟以及自己分步的时钟。 1.1 输入时钟 输入时钟是指时钟从FPGA管脚进来的情形,这也是最常见的情况。根据输入的管脚的不同,输入时钟情况又可以分成:输入管脚是单端的、输入管脚是差分的,以及GT或者恢复时钟三种情况。 第一种:输入管脚是单端的,即时钟直接从管脚进来、并且是单端信号。例如普通低速晶振,大部分是这种情况,明德扬的FPGA ALTERA学习板,如MP801、MP603,其时钟均是由晶振产生,送到FPGA,并且是单端的信号。 第二种:输入管脚是差分的,即时钟直接从管脚进来,并且是差分信号。大部分高速晶振、LVDS接口等,属于此情形。例如明德扬FPGA XILINX学习板,如MP802,其包含了PCIE管脚,其输入的时钟就是差分的;这个板子的DDR的驱动时钟,时钟频率在200M左右,也是属于此种以情形。 第三种:GT或者恢复时钟,即使用了高速收发器的情形。在高速收发器管脚中,是没有时钟的,时钟已经嵌入到数据里面,使用FPGA的GTX IP核接收数据,并且从数据恢复出时钟。这个恢复出来的时钟就是此种情形。最常见的就是光纤接口。 1.2 PLL等衍生时钟 那假如说我不是输入管脚,而是PLL产生的输出时钟,这个 就是PLL等衍生时钟。这种时钟,FPGA的工具,会自行推导,一般无需约束,但实质应用中,强烈建议约束,会有好处的,好处在下一篇文章中说明。 1.3 自己分频的时钟 还有一种情况是自己分频的时钟,假如说我们自己写了一个计数器,把它二分频、四分频、八分频等,分频出来的信号当为时钟,这种情况就是自己分频的时钟。 首先说明,明德扬不推荐使用此方法来产生时钟。但确实要用到分频时钟时,那就要记得做时钟约束。这种情况下要怎么进行约束呢? 以上概括了说明了时钟的几种情况,每种情况下,其约束方法都有些不同以及注意点。具体约束方法,可以看后续文章的内容。 第2节 input delays input delay约束,即输入延时约束,是时序约束的重点,input delay 又分几种呢?

如上图,input delay约束概括地,可以分成三种情况,分别是系统同步、源同步和有数据无时钟。 2.1 系统同步 第一个是系统同步方式,也就是说整个电路板上FPGA以及上游器件都共用一个时钟,并且相位严格相同,这个就是系统同步的方式。 2.2 源同步 第二种是源同步的方式,源同步是怎么样?就是上游器件,把数据和时钟信号一起送到FPGA上来的,那这种就是源同步。 源同步是更常用的一种方式,系统同步比较少用,为什么呢?因为要做到上游器件跟FPGA的相位差为0,没有一点时钟差,这种要求非常高。而源同步是数据跟时钟都是从上游器件一起输送过来给FPGA,这是一种更常用的方式。 这个源同步,又有很多种,具体SDR、DDR和有数据无时钟三种情况。 第一种:SDR。SDR是指时钟是单沿有效的方式,比如说我只用上升延或者下降延的一个方式,SDR约束的参数,其获取的方法有两种:查看上游器件手册(通过查看上游器的数据手册,获取参数)以及通过示波器测量(通过示波器测量信号的相位差,获取参数)。 第二种:DDR。DDR是另一种方式,它是一种时钟双沿有效的一个方式。也就说即用它的上升延,也用它的下降延。例如说我们的DDR2、DDR3的时钟,都是上下降沿一直采数据的;包括千兆网的RGMII接口,也是通过双沿的方式。 DDR的这种情况,我们还可以继续划分成中心对齐和边沿对齐两种情况。 中心对齐是指:时钟边沿始终在数据的中间,时钟上升沿的左右两边,数据都是稳定的。边沿对齐是指:时钟和数据边沿对齐的,在时钟变化沿两边,其数据是不稳定的。 第三种:有数据无时钟。第三种就是有数据无时钟的情况。例如说常见的串口。串口是直接数据过来的,它是没有随路时钟过来的。而我们用本地时钟去采样,就会出现有数据无时钟。那对于这种我们应该怎么去约束,又是另一种情况。 第3节 output delays 输出延时约束和输入延时一样,也是约束的重点。output delay 我们主要分两种,系统同步和源同步。

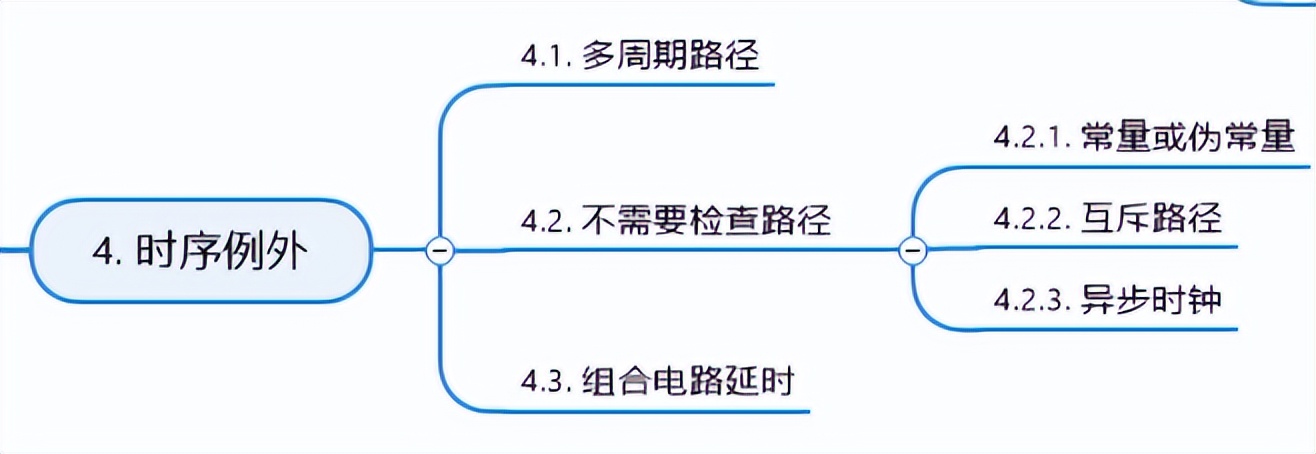

3.1 系统同步 整个电路板上FPGA以及下游器件都共用一个时钟,并且相位严格相同,这个就是系统同步的方式。此时FPGA往下游器件发送数据,这时候只传送数据线就可以了。而时钟跟FPGA共用一个的,不需要传时钟。 3.2 源同步 源同步就是FPGA往这个器件发数据,在发数据过程中也发一个时钟过去,这是一个随路时钟的一个方式,是源同步。 源同步我们还分SDR和DDR。 第一种:SDR。SDR是指时钟是单沿有效的方式,比如说我只用上升延或者下降延的一个方式,SDR约束的参数,其获取的方法有两种:查看上游器件手册(通过查看上游器的数据手册,获取参数)以及通过示波器测量(通过示波器测量信号的相位差,获取参数)。示波器测量比较少用。 第二种:DDR。DDR是另一种方式,它是一种时钟双沿有效的一个方式。也就说即用它的上升延,也用它的下降延。例如说我们的DDR2、DDR3的时钟,都是上下降沿一直采数据的;包括千兆网的RGMII接口,也是通过双沿的方式。 DDR的这种情况,我们还可以继续划分成中心对齐和边沿对齐两种情况。 中心对齐是指:时钟边沿始终在数据的中间,时钟上升沿的左右两边,数据都是稳定的。边沿对齐是指:时钟和数据边沿对齐的,在时钟变化沿两边,其数据是不稳定的。 第4节 时序例外 时序例外一般用在clock与IO都约束后,还是不满足时序要求的情况下。主要包括多周期路径、不需要检查的路径和组合电路延时等三种情况,如下图。

4.1 多周期路径 多周期路径是指完成一个运算需要超过1个时钟周期的情形,多周期路径在IC设计领域运用较多,但在FPGA里应用较少。 4.2 不需要检查的路径 有一些路径是不需要分析的,具体可以分成三种:常量或伪常量信号、互斥路径和异步时钟。 第一种:常量或伪常量信号。某些信号虽然不满足时序要求,但实质上该信号在应用场景中,是不会改变的,例如某个开关信号,它在上电时打开后,就一直保持打开状态,不会变来变去。那么这个信号就可以认为是伪常量信号。假设它不满足时序要求,也是无所谓的,因为不会变,不会变就意味着建立时间和保持时间肯定满足,所以不存在问题。这种信号是不需要检查 的。 第二种:互斥的路径。可以简单认为是双向端口,即代码中,使用inout定义的信号。 第三种:异步时钟。即信号从一个时钟域,跨到另一个时钟域的情况。这也是不需要检查 的。注意,这里说不用检查,是指完成异步信号同步化后,不用检查的意思。 4.3 组合电路延时 还有一种是组合电路的延时。组合电路延时就是说我从这个管脚到另一个管脚之间,另一个管脚进来,这个管脚出去中间没有任何一个时钟,这是组合电路给延时的一种情况。 第5节 总结与建议 前面我们讲了时钟约束、输入延时、输出延时还时序例外的情况。每一种情况又分了很多种,根据它的不同类型来区分,每次约束的时候都是其中的一种情况。比如说CLK差分,就去找时钟,然后根据差分管脚怎么约束,来找到对应情况,按照要求进行约束。这相当于我已经提供一个表给你,你按照这个表去核对。找到对应的情况,按要求进行约束就可以了。 记住:开始的时候,只是配置时钟,不配置input delay 、 output delays和持续例外。因为我们开始的时候是专心于内部电路,我们时序的一个设计,满足内部要求之后,再去配置我们的接口。在时钟完全通过之后再配置input delay 和output delays 。 时序例外是最后差不多要完工了再进行配置的。而且这个配置是要很小心。因为我们实际例外,比如说不用检查,我们set false path这种情况,设置好就是表示不用检查。如果在开始的时候,就设置好了,万一中间又要改变,你改变的话,那你忘了把这个约束给干掉了,这种情况就会出现有错误也提示不出来的情况。所以说时序例外应该是最后情况下进行的。 这个顺序是明德扬经验的一个顺序,我们的项目基本上是按照这个顺序做的。但是不同的公司也会有不同的做法。例如说我一开始全部都不约束,到最后再生约束,这也是可以的。这种做法没有统一标准,反正学明德扬的课程,你就按这个步骤做,去到其他公司,再根据公司要求去做就可以了。 本文章是基于赛灵思的一个时序约束,ALTERA也是相似的,甚至IC芯片设计领域,也是同样的思路。 有句话讲的很好,我们的时序是设计出来的,不是约束出来的。所以说时序重要还是不重要?当然重要。但是它不是非常重要,更重要的是假如说我时序出现例外,不满足的时候,更重要是改变你的设计,而不是要求约束。 下一篇文章,我们将具体探讨“时钟约束”的内容,讲解各种情况下的时序约束方法。需要更多更详细的资料和原文档的,可以找作者了解和领取。 明德扬(MDY)除了培训课程外,还可为客户提供承接项目、FPGA芯片、电源芯片、AD芯片等元器件,可找我们了解。18922344178(电话微信同步) 作者:明德扬FPGA科教

|

/1

/1

|手机版|OpenEdv-开源电子网

( 粤ICP备12000418号-1 )

|手机版|OpenEdv-开源电子网

( 粤ICP备12000418号-1 )