|

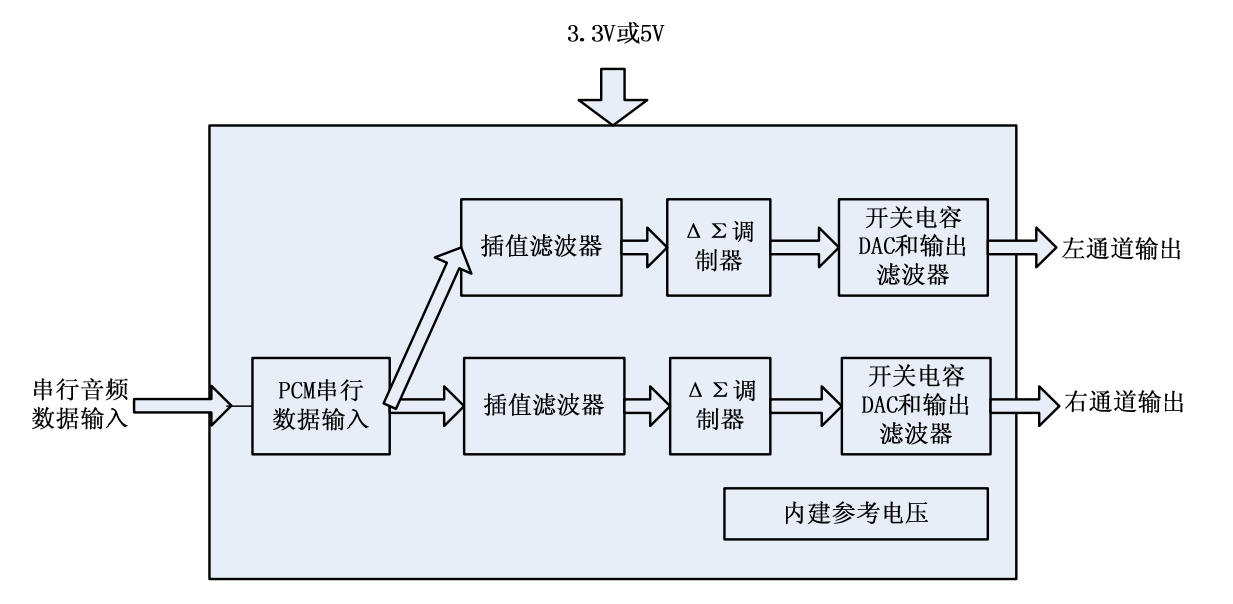

MS4344描述 MS4344是一款立体声数模转换芯片,内含插值滤波器、multi bit数模转换器、输出模拟滤波器。MS4344支持大部分的音频数据格式。MS4344基于一个带线性模拟低通滤波器的四阶multi-bitΔ-Σ调制器,而且本芯片可以通过检测信号频率和主时钟频率,在2KHz 和200KHz 之间自动调节采样率。 MS4344可以工作在3.3V和5V下。这些特性使它成为DVD播放解码器、数字通信设备等无线设备的理想选择。 MS4344 采用 MSOP10 封装。 主要特点 Muti-bitΔΣ调制器 24bit D/A 转换器 自动检测最大到 192KHz 的信号频率 110dB 动态范围 0.003% 总谐波失真 低时钟抖动敏感度 3.3V 或 5V 工作电压 线性滤波输出 应用 数字通讯设备 汽车音响系统 DVD 音频系统 内部框图

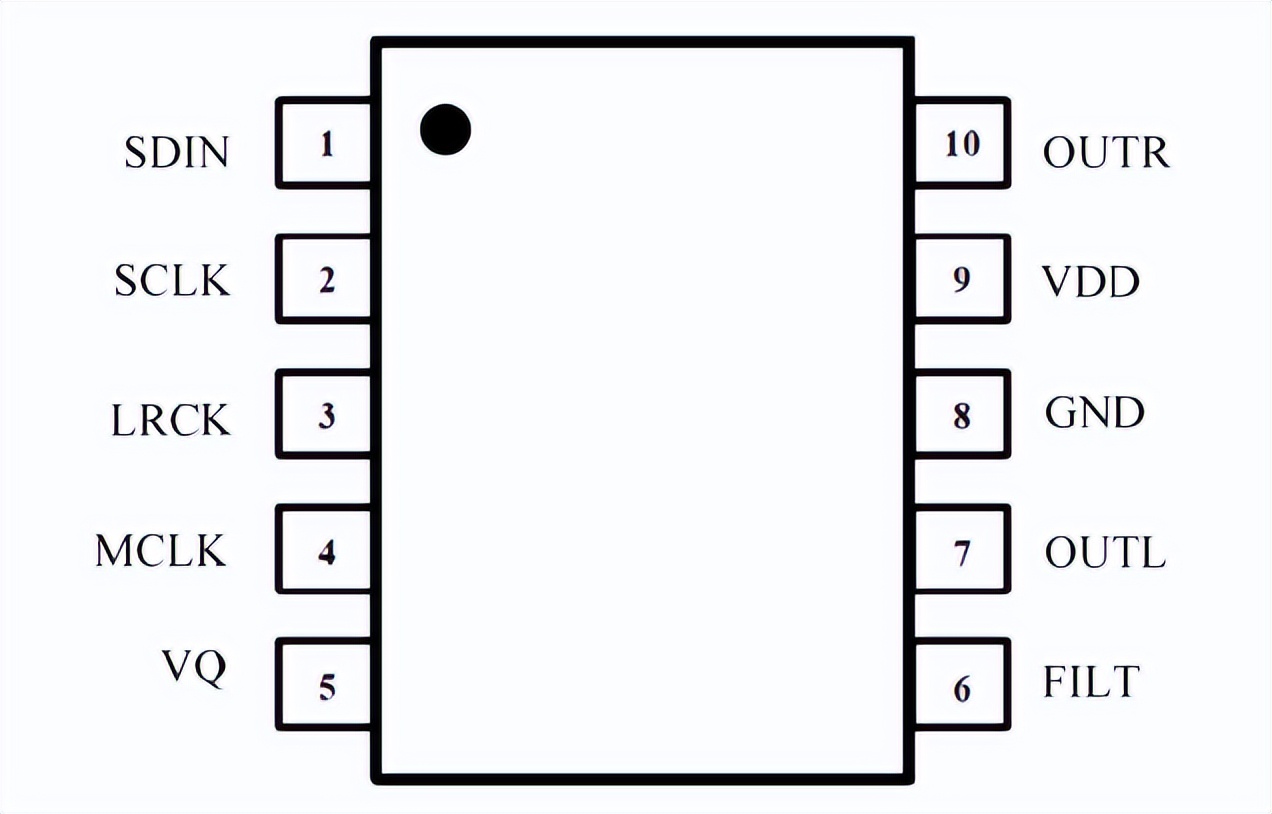

管脚图

管脚说明图

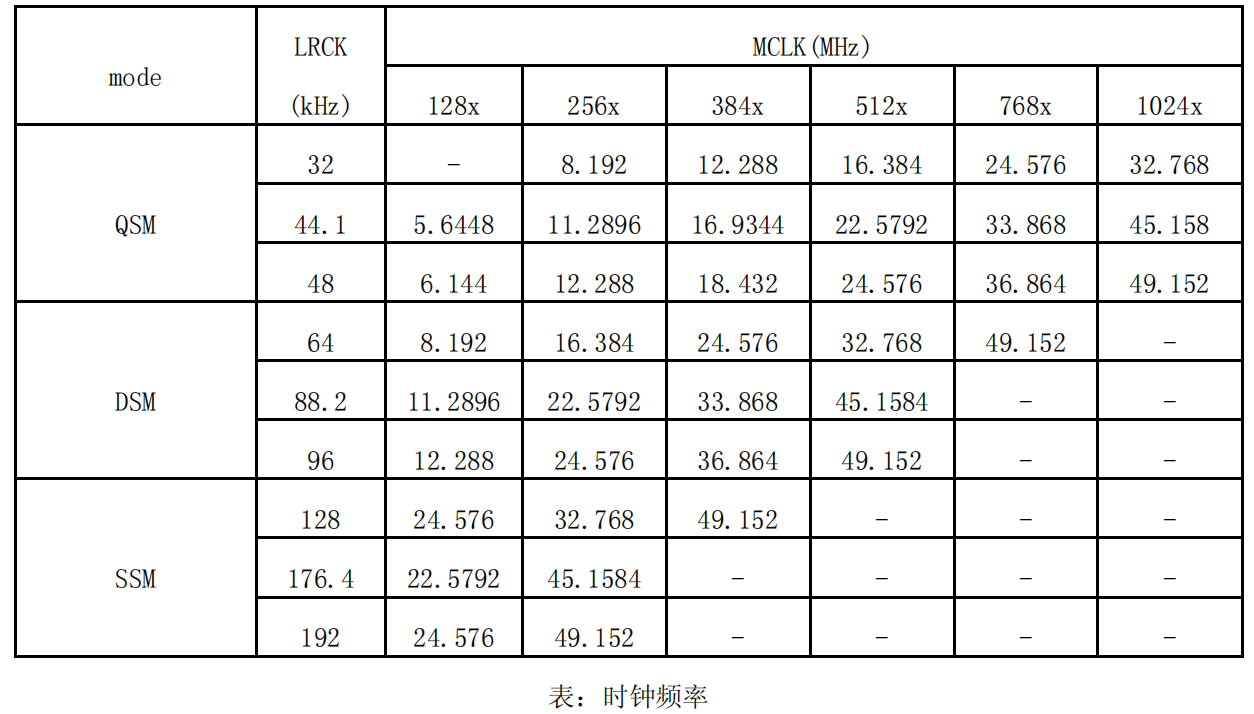

功能描述 MS4344 接受标准的音频采样频率,包括在QSM 模式下的48、44.1、32kHz,在DSM 模式下的96、88.2、64kHz,在SSM 模式下的192、176.4、128kHz。音频数据通过串行输入数据端输入(SDIN)。左/右通道时钟(LRCK)决定当前输入数据的通道。串行时钟是音频数据进入输入数据缓存的时钟。 主时钟 MCLK/LRCK 的比值必须是整数,见下表。LRCK 的频率等于每个通道输入数据的频率Fs。MCLK与LRCK 的比值和速度模式是在初始化时通过计算在一个LRCK 周期内MCLK 的周期数以及MCLK 的值来决定的。内置的除法器会产生合适的时钟。下表 列出了一些音频采样频率,以及相应的MCLK 和LRCK频率。请注意这里虽然没有相位的要求,但是LRCK 和MCLK 必须同步。

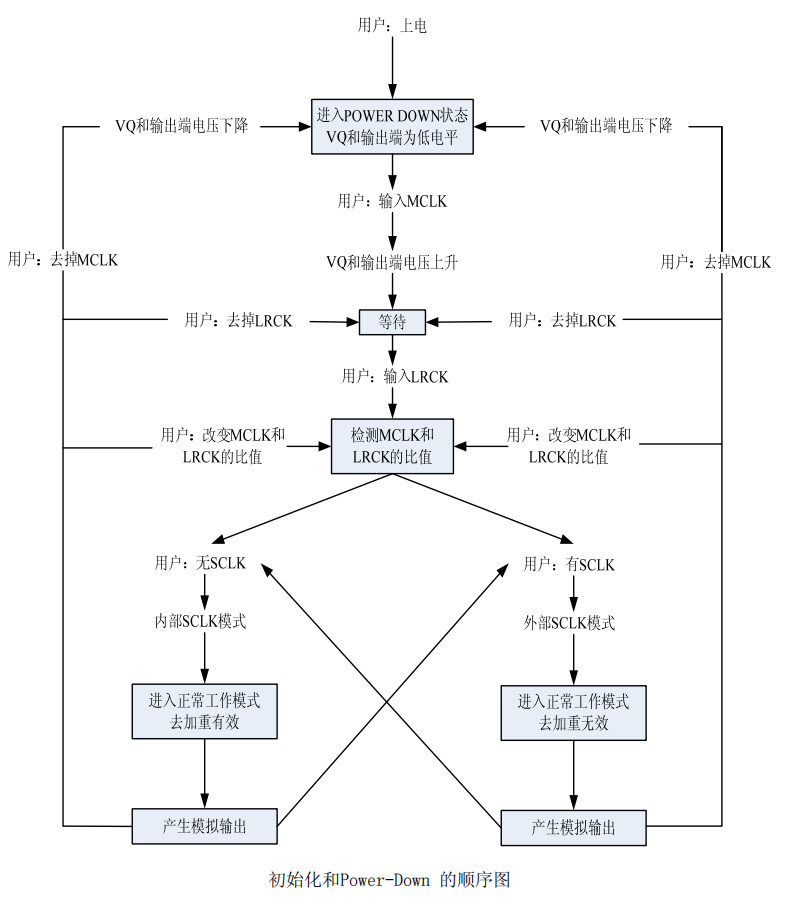

初始化和Power-Down 当系统初始上电后就进入 power-down 状态,此时插值滤波器和ΔΣ调制器复位,内部参考电压、数模转换器、开关电容滤波器、低通滤波器被关闭,直到系统检测到 MCLK 和 LRCK 时钟。一旦 MCLK和 LRCK 被检测到,系统就开始计算 MCLK 和 LRCK 的比值,然后给内部参考电压上电,最后才给数模转换器、开关电容滤波器上电,同时输出端输出静态电压 VQ。 输出瞬态控制 MS4344 采用Pop-guard 技术来减小上电和下电时的瞬态响应。 上电 输出端的直流电平就由 VQ 端提供,当系统初始上电时,VQ 端为低电平。当MCLK 检测到后,VQ端产生正常的直流电压。当VQ 端接10uF 电容需400ms的启动时间。 下电 为了防止在下电时输出端产生瞬态脉冲,VQ端外接10uF电容,以保证MCLK在下电前停止,在这段时间内VQ 端和输出端逐渐下降到GND。当需要改变时钟频率或采样频率时,最好在LRCK保持10个周期的低电平信号。在时钟变换的过程中,DAC将保持低电平输出。 初始化和power down流程如下图所示:

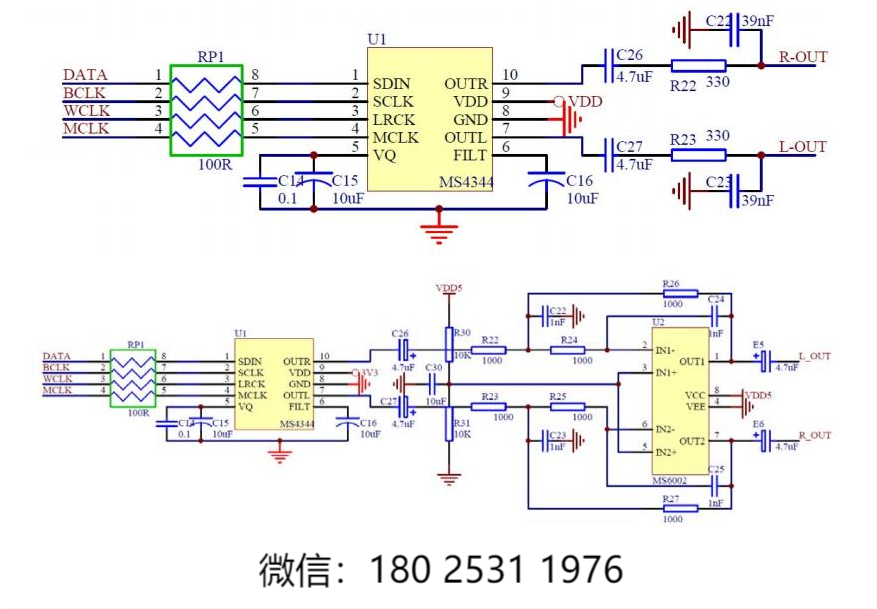

接地与电源去耦合 MS4344 地与电源的连接必须非常注意以达到理想的性能。为了得到最好的性能,去耦合与滤波电容必须尽可能的靠近芯片。 典型应用图

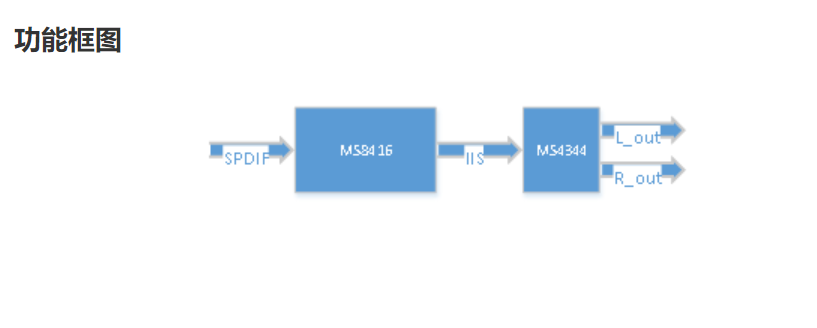

MS8416+MS4344数字音频接口解决方案

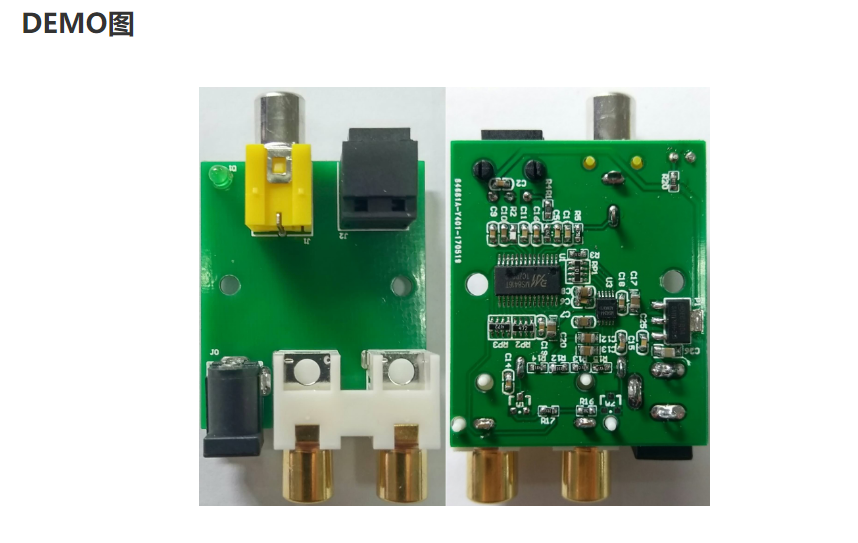

本DEMO板使用5VDC供电。 当图1左下插入5VDC电源后左上角绿色LED点亮。 支持两种SPDIF信号接口,分别为同轴信号和光纤信号。 图1中上黄色RCA接口(J1)为SPDIF同轴输入。 图1右上黑色接口(J2)为SPDIF光纤输入。 本模块自动识别插入的信号源,但是当两个信号同时输入时,将发生异常。 模拟立体声从下部RCA输出,白色为左声道,红色为右声道。

|

/1

/1

|手机版|OpenEdv-开源电子网

( 粤ICP备12000418号-1 )

|手机版|OpenEdv-开源电子网

( 粤ICP备12000418号-1 )