|

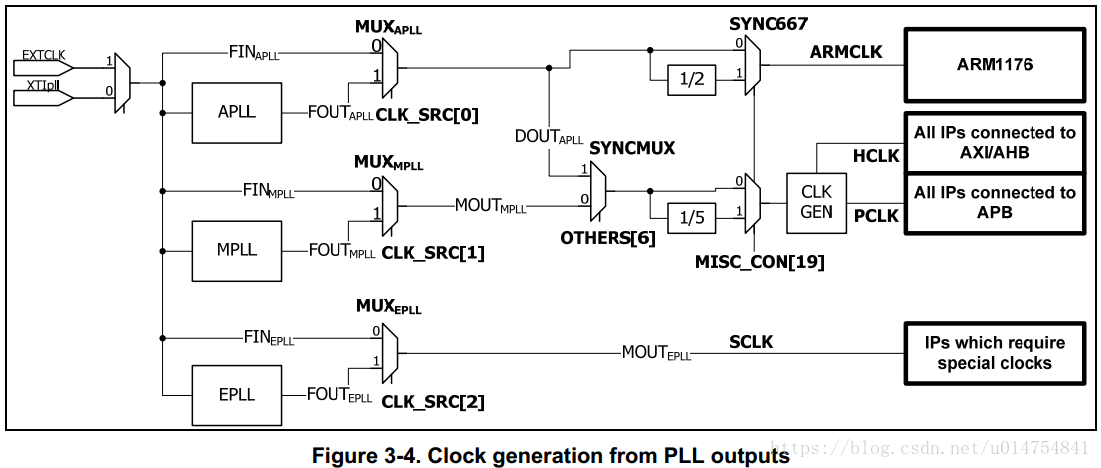

接上。。。 6.时钟初始化:bl init_clock S3C6410可以使用外部晶振( XXTIpll )(默认为12MHZ)和外部时钟( XEXTCLK )两种方式输入时钟信号。它由跳线OM[0]决定。 S3C6410 默认的工作主频为12MHz(晶振频率), 3sc6410的系统时钟逻辑控制器可以产生系统必须的三种时钟信号,ARMCLK for CPU, HCLK for AXI/AHB-bus peripherals, and PCLK for the APB bus peripherals。s3c6410共有三种PLL,其中APLL用于产生ARMCLK,MPLL用于产生HCLK和PCLK,EPLL用于产生SCLK,音频相关的时钟,如下图:

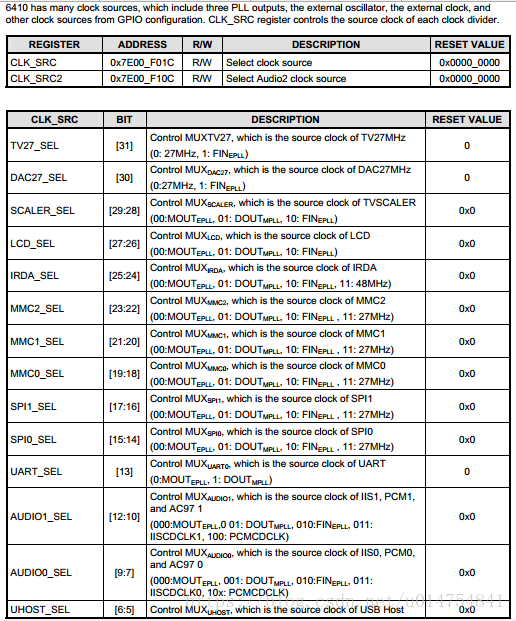

框图下面有一段话,说明CLK_SRC寄存器是需要设置的,用来选择时钟输出源,如下:

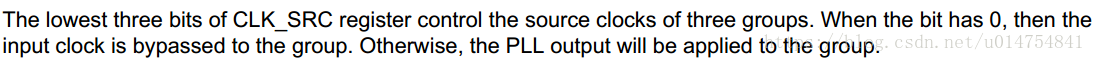

下面的框图说明了系统时钟配置需要设置那些寄存器和如何设置参数,如下:

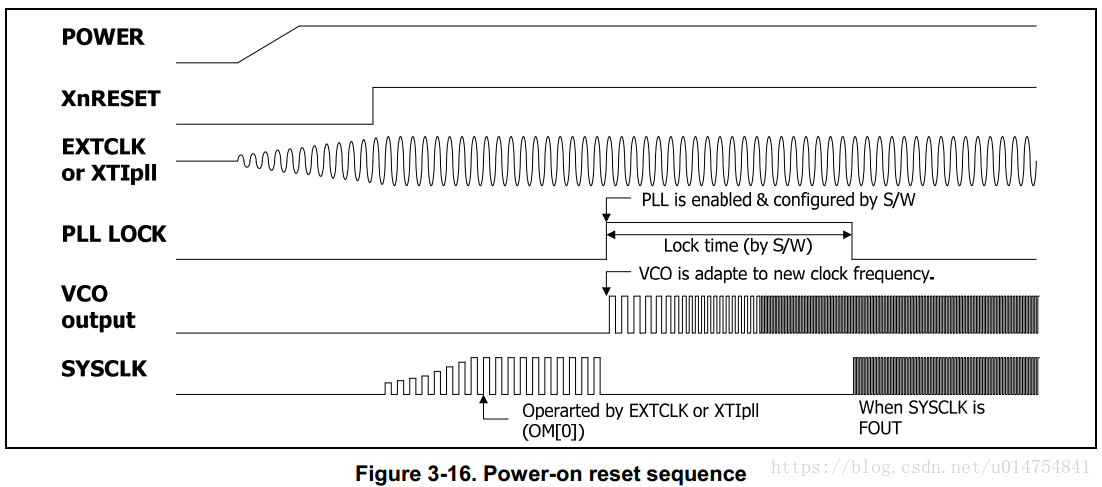

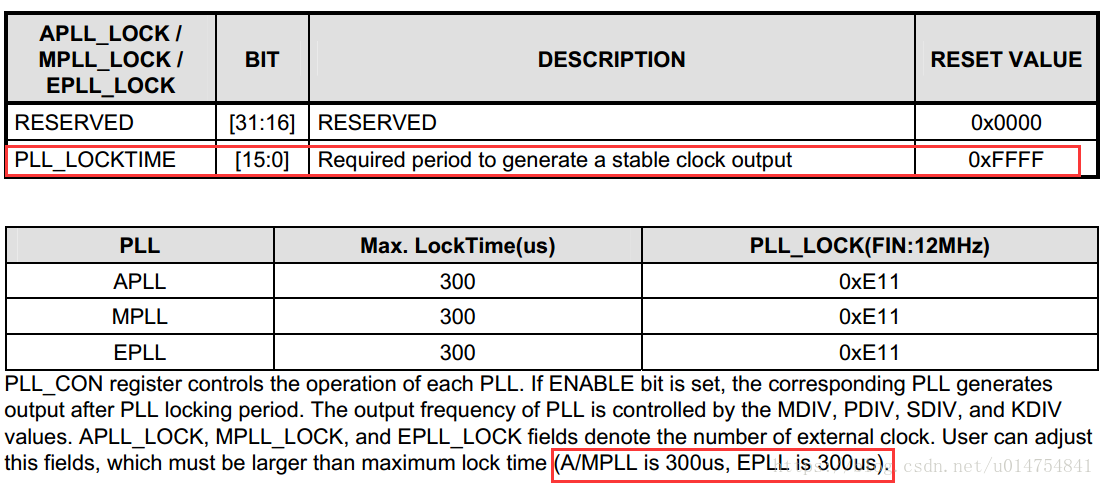

除了上面提到的寄存器需要配置,当然也少不了APLL控制寄存器和MPLL控制寄存器了,下面介绍一下这些寄存器。 从上图Power-on reset sequence中看到有一个Lock time,在这段时间(Lock Time)内,FCLK停振,CPU停止工作。Lock Time的长短由寄存器LOCKTIME设定 ,Lock Time之后,MPLL输出正常,CPU工作在新的FCLK下。 所以这个参数需要设定,但是由于这个时间很短(只有300us),所以不设定也不影响使用,如下图:

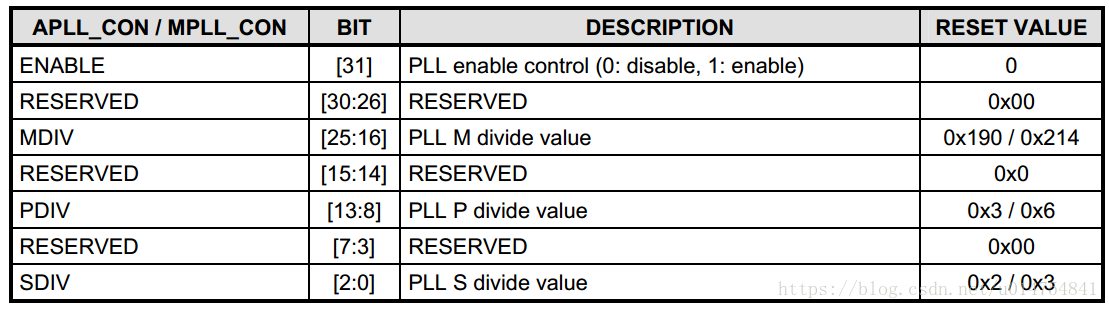

APLL_CON和MPLL_CON说明如下:

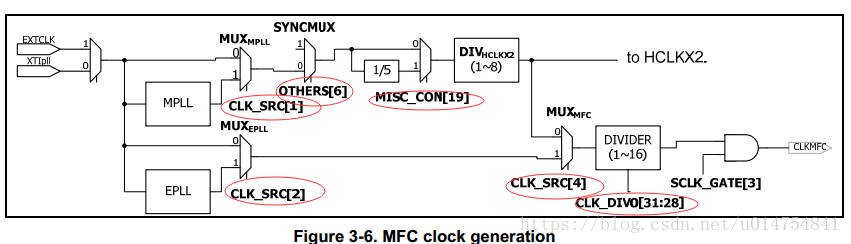

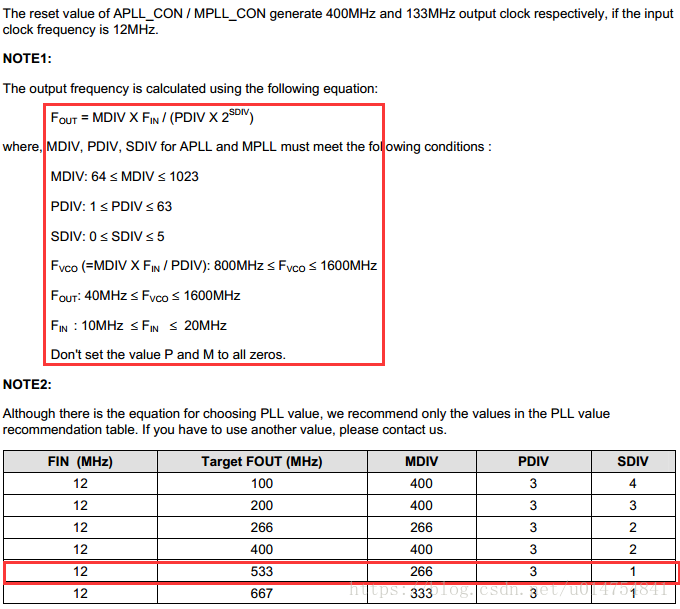

从上图可知,只需设置SDIV、PDIV、MDIV、ENABLE位就可以了,参考设定值如下:

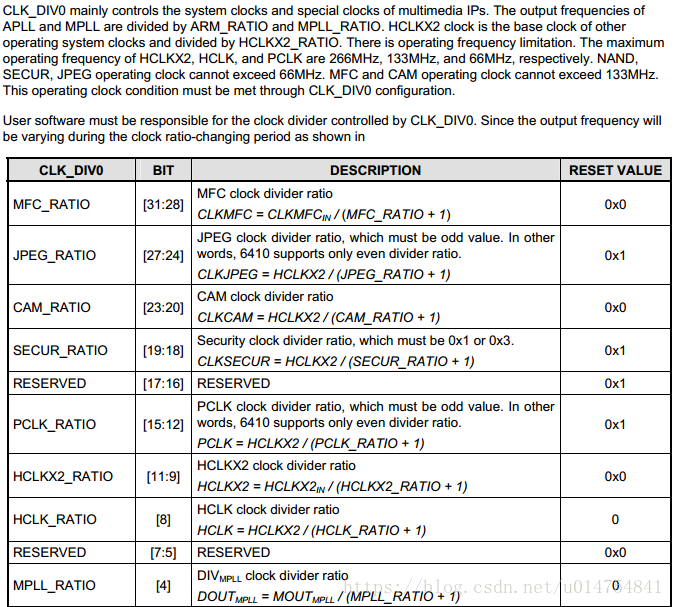

CLK_DIV0寄存器说明如下:

用于设定ARMCLK、PCLK、HCLK等。 CLK_SRC说明如下:

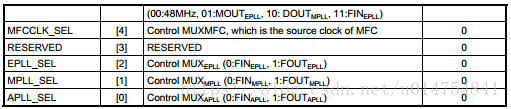

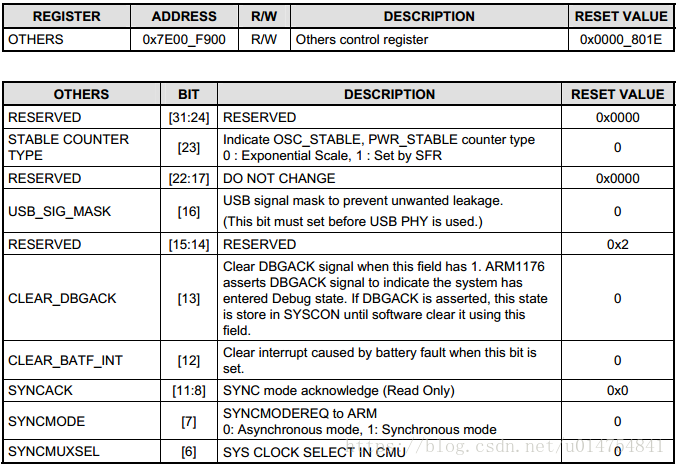

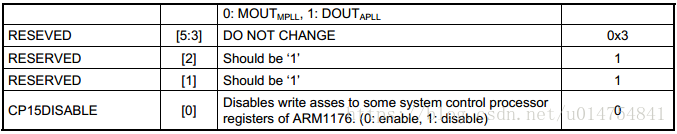

这里只需要设定[2:0]就可以。 OTHERS寄存器说明如下:

这里我们只需设定[7:6]即可。代码如下: @ 初始化时钟 参考s3c6410手册系统控制章节、时钟相关章节#define CLK_DIV0 0x7e00f020 @ 时钟分频寄存器0地址#define OTHERS 0x7e00f900 @ 其他控制寄存器地址#define MPLL_CON 0x7e00f010 @ MPLL控制寄存器地址#define APLL_CON 0x7e00f00c @ APLL控制寄存器地址#define CLK_SRC 0x7e00f01c @ 时钟源选择寄存器地址#define DIV_VAL ((0x0<<0)|(0x1<<9)|(0x1<<8)|(0x3<<12)) @ 分频设置值 2b0000_0000_0000_0000_0011_0011_0000_0000 参考uboot设置#define PLL_VAL ((1<<31)|(266<<16)|(3<<8)|(1<<0)) @ PLL设置值 2b1000_0001_0000_1010_0000_0011_0000_0001 参考uboot设置init_clock: @ 设置时钟分频系数 ldr r0, =CLK_DIV0 @ 将时钟分频寄存器0的地址存入寄存器r0中 ldr r1, =DIV_VAL @ 将需要配置到时钟分频寄存器0的数值存入寄存器r1中 str r1, [r0] @ 将r1的数值传送到时钟分频寄存器0中 @ 设置cpu为异步模式,将OTHERS寄存器内容设置为0xc0 ldr r0, =OTHERS @ 将OTHERS寄存地址存入寄存器r0中 ldr r1, [r0] @ 将其他控制寄存器中的数据读出,存入r1中 bic r1,r1,#0xc0 @ 将r1中的数值第6 7 bit位清0后再存入r1中 str r1, [r0] @ 将r1中的数值传送到OTHERS寄存器中,Asynchronous mode 和 MOUTmpll @ 设置APLL时钟频率 533MHz ldr r0, =APLL_CON @ 将APLL控制寄存器地址写入r0中 ldr r1, =PLL_VAL @ 将需要配置的PLL数值存入寄存器r1中 str r1, [r0] @ 将r1中的数值写入APLl控制寄存器中 @ 设置MPLL时钟频率 533MHz ldr r0, =MPLL_CON @ 将MPLL控制寄存器地址写入r0中 ldr r1, =PLL_VAL @ 将需要配置的PLL数值存入寄存器r1中 str r1, [r0] @ 将r1中的数值写入MPLL控制寄存器中 @ 设置时钟源选择控制寄存器,使用APLL和MPLL输出时钟。 ldr r0, =CLK_SRC @ 将时钟源选择寄存器地址写入r0中 mov r1, #0x3 @ 将0x03写入寄存器r1中 str r1, [r0] @ 将r1中的数据写入时钟源选择控制寄存器中 mov pc, lr @ 返回调用处继续往下执行

|

/1

/1

|手机版|OpenEdv-开源电子网

( 粤ICP备12000418号-1 )

|手机版|OpenEdv-开源电子网

( 粤ICP备12000418号-1 )