终于到第九讲了,第九讲是这套《轻松设计SDRAM控制器》的最后一讲。

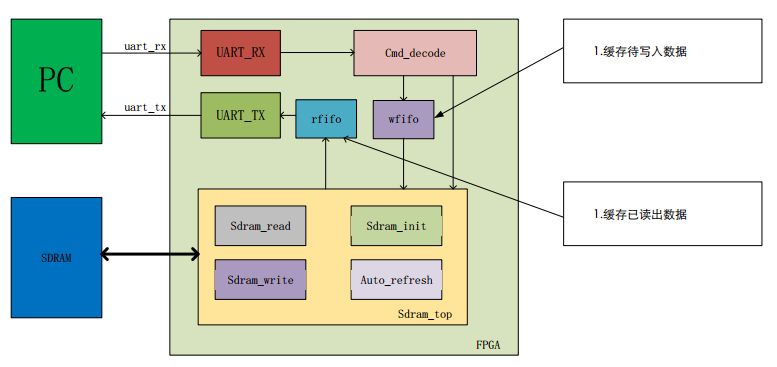

相信大家也是非常的期待这套教程的终结,在前面的8讲内容,我们已经介绍完了SDRAM控制器、串口部分和命令解析模块。

在第九讲中,我们主要是来介绍如何引入读写FIFO。

本讲主要内容如下:

- 读写FIFO的作用;

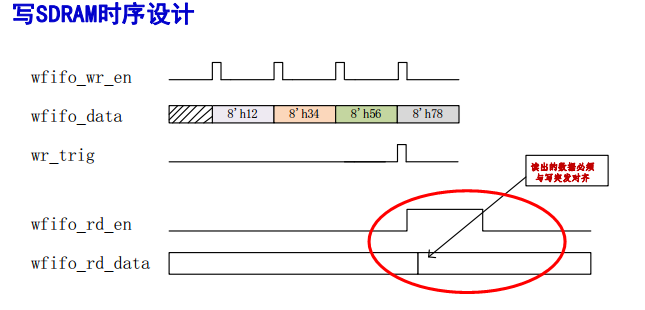

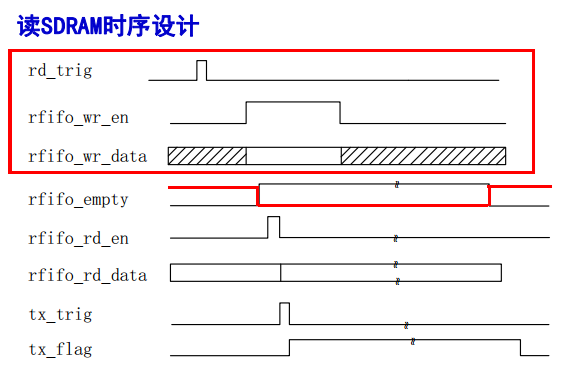

- 读写FIFO的时序设计;

- 完整项目的代码整合及调试。

一、读写FIFO的作用

记得Kevin曾经在【开源骚客】公众号里边做过这样一个互动,大家可以给公众号的后台发送自己对于读写FIFO作用的理解。

当然还是有很多网友给后台发送过自己的理解,正确率应该是60%左右。

使用读/写FIFO的原因:

1.写SDRAM, 串口发送4个字节的数据所需时间太长, 而SDRAM写入数据的时间极短, 需使用FIFO缓存待写入的数据; 2.读SDRAM, 需将从SDRAM中读出的数据发送到上位机, SDRAM读出速度远大于串口发送数据的速率, 需使用FIFO缓存已从SDRAM中读出的数据。 二、读写FIFO的时序设计

对于串口发送过来的是待写入的数据时,我们是在当串口接收到了第四个待写入的数据时(待写入数据的最后一个),才向SDRAM控制器产生写出发命令。

虽然在时序图总都已经设计好了读/写FIFO的各个信号,但是这仅仅只是关于两个FIFO的信号而已。

这些信号和SDRAM控制器关联起来,这就是需要花时间慢慢琢磨的。

三、完整项目的代码整合及调试对于完整项目的代码调试,过程相当繁琐,Kevin就不在电子版中进行讲解了(毕竟语文是数学老师教的。。。/捂脸)。

对于完整项目的调试,强烈建议大家观看《轻松设计SDRAM控制器》的第九讲视频。

四、最后的话Kevin之前在网络上看到过这样的一种观点,“免费,永远也学不会”!

但是照目前的状况来看,《轻松设计SDRAM控制器》这套教程从发布第一讲到现在,已经快半年的时间了,看到在开源骚客的QQ交流群中跟着我们的教程设计出SDRAM控制器的朋友越来越多,那种“免费,永远也学不会”的观点也些许有些片面。

当然,对于这种观点,也是不无道理的。

- 对于免费的东西,教程提供方可能会由于自身的某些原因,导致免费分享出来的教程不够详细。

- 作为免费教程的受众方,我们对于免费的东西就不会太在意,不会强迫自己去学习,毕竟自己也没花多大的代价来获得已有免费的资源。

但是对于《轻松设计SDRAM控制器》这套教程,是Kevin通过对当时在上海进行学习并经过工作中项目的锻炼后,在有深刻理解下根据自己的方式总结并分享出来的。

《轻松设计SDRAM控制器》这套教程,虽免费,但价值巨大,只要你跟着教程走,有问题及时加群进行请教,Kevin是有理由向你保证绝对可以学会的。

另外,对于SDRAM控制器的完整代码,Kevin没有免费分享出来。

如果你想获取SDRAM控制器的代码,可以向【开源骚客】公众号后台直接发送“SDRAM”便可以了解到代码的获取方式。

重磅惊喜:《SDRAM那些事儿 第一季-轻松设计SDRAM控制器》虽已完结,但在今年的3月底,Kevin将继续分享《SDRAM那些事儿 第二季》教程。

第二季教程依然采取项目形式免费分享,力争花两个月的时间分享结束,给18届的应届毕业生提供一个提升校招的核心竞争力!!!

|

/1

/1

|手机版|OpenEdv-开源电子网

( 粤ICP备12000418号-1 )

|手机版|OpenEdv-开源电子网

( 粤ICP备12000418号-1 )